성균관대, 3D 반도체 소자 기술 개발…네이처 게재

3D 소자 기술로 2D 반도체 집적도 한계 극복

18일 국제학술지 네이처(Nature) 게재

"인공지능·IoT 등 첨단기술 분야서 중요한 역할 할 것"

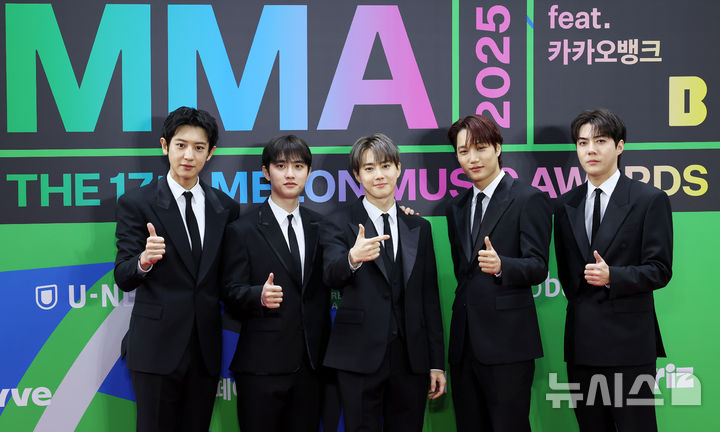

(왼쪽부터) 박진홍 교수, 김기석 박사, 서승환 박사, 전종욱 교수, 안호근 연구원, 정항교 연구원. (사진=성균관대 제공) *재판매 및 DB 금지

이번 연구는 10옹스트롬(1나노미터) 이하 기술 노드에 고려되고 있는 소자 기술을 개발하기 위해 이뤄졌다. MIT의 김지환 교수팀, 삼성종합기술원(SAIT)의 김상원·설민수 박사 연구팀이 함께 참여했다.

기존 3D 반도체 기술에서는 실리콘 웨이퍼를 관통하는 TSV(Through-Silicon Via) 방식이 주류였다. TSV 방식은 웨이퍼 간 정렬 오류, 높은 공정 비용, 칩 면적 손실 등 여러 단점을 갖고 있었다.

연구팀은 이를 극복하기 위해 웨이퍼 간 물리적 연결 없이 단결정 전이금속 디칼코제나이드(TMD) 채널을 성장시키는 '모노리식(Monolithic) 3D 집적 방식'을 택했다. 이 방식은 소자의 성능을 극대화하면서도 물리적 연결을 최소화해 공정 효율성과 집적도를 동시에 개선할 수 있다.

박진홍 교수는 "이번 연구는 기존 TSV 기술을 넘어서는 혁신적인 기술적 진전을 이뤄낸 사례"라며 "모노리식 3D 집적 방식으로 저온 공정에서 단결정 소자를 직접 성장시켜 3D C-FET 반도체 집적 기술을 실현한 것은 중요한 기술적 도약"이라고 전했다.

이어 "이 기술은 에너지 효율을 극대화하는 데도 기여할 수 있을 것"이라며 "향후 인공지능·데이터 센터·IoT 등 다양한 첨단 기술 분야에서 중요한 역할을 할 것"이라고 덧붙였다.

한편 이번 연구 결과는 지난 18일 저명 학술지 네이처(Nature)에 게재됐다. 해당 기술이 반도체 소자의 집적도 향상과 제조 공정 혁신을 통해 무어의 법칙(Moore's Law)의 한계를 극복할 수 있을지 주목을 모으고 있다.

◎공감언론 뉴시스 [email protected]

Copyright © NEWSIS.COM, 무단 전재 및 재배포 금지