성균관대-GIST 공동연구팀, 차세대 수직 트랜지스터 개발

불필요한 전류 억제…트랜지스터 성능 1000배 향상

차세대 초소형 반도체 기술 상용화 기대

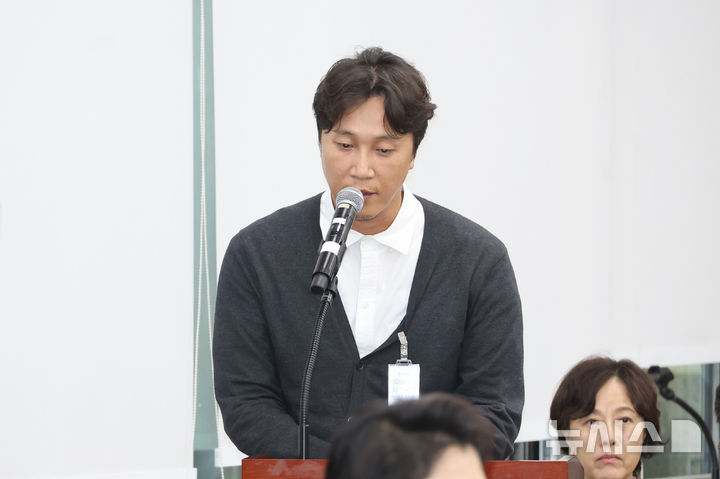

![[서울=뉴시스] (왼쪽 위부터 시계방향으로) 성균관대 강보석 교수, 광주과학기술원 김현호 교수, 금오공대 최다은 석사과정생, 성균관대 최현규·박효광 박사과정생. (사진=성균관대 제공) 2025.10.13. photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2025/10/13/NISI20251013_0001964669_web.jpg?rnd=20251013154649)

[서울=뉴시스] (왼쪽 위부터 시계방향으로) 성균관대 강보석 교수, 광주과학기술원 김현호 교수, 금오공대 최다은 석사과정생, 성균관대 최현규·박효광 박사과정생. (사진=성균관대 제공) 2025.10.13. [email protected] *재판매 및 DB 금지

트랜지스터는 전자기기의 동작 속도와 에너지 효율을 결정짓는 핵심 부품으로, 작고 빠를수록 성능이 우수하다. 이에 반도체 산업은 트랜지스터의 크기를 지속적으로 줄여왔다.

이러한 기술 발전 흐름은 '무어의 법칙(Moore's Law)'으로 설명된다. 무어의 법칙은 트랜지스터의 집적도가 약 2년마다 2배씩 증가한다는 개념이다.

수직 트랜지스터는 2차원 소재를 활용해 원자 수준의 초소형 구조를 구현할 수 있어 차세대 소자로 주목받고 있으나, 설계 구조상 일부 영역에서 불필요한 전류가 흘러 성능이 떨어지는 문제가 있었다.

이에 연구팀은 새로운 반도체 물질인 이셀레늄화몰리브덴(MoSe₂)을 채널로 도입했다. 이 물질은 특수 열처리 과정을 통해 전자의 흐름을 정밀하게 조절할 수 있도록 설계됐으며 이를 통해 트랜지스터 내부에서 발생하는 누설전류를 억제하는 데 성공했다.

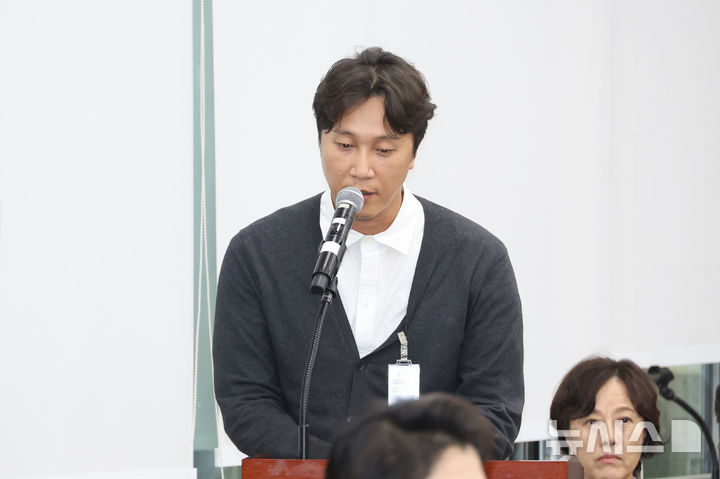

![[서울=뉴시스] 게이트 비인가영역에서의 누설 전류를 억제하여 구현한 고성능 수직 트랜지스터. (사진=성균관대 제공) 2025.10.13. photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2025/10/13/NISI20251013_0001964674_web.jpg?rnd=20251013155034)

[서울=뉴시스] 게이트 비인가영역에서의 누설 전류를 억제하여 구현한 고성능 수직 트랜지스터. (사진=성균관대 제공) 2025.10.13. [email protected] *재판매 및 DB 금지

강 교수는 "이번 연구는 수직 트랜지스터에서 오랫동안 해결되지 않았던 누설전류 문제를 근본적으로 해결한 사례"라고 설명했다.

이번 연구는 산업통상자원부와 과학기술정보통신부의 지원을 받아 수행됐으며 나노과학 분야의 세계적 권위지 'ACS 나노(Nano)'에 게재됐다.

◎공감언론 뉴시스 [email protected]

Copyright © NEWSIS.COM, 무단 전재 및 재배포 금지