TSMC, 후공정 통합 파운드리 1위…'패키징'도 격차 벌린다

TSMC, 후공정 점유율 35.3%

CoWoS 등 첨단패키징 기술력 증명

삼성, 점유율 5%대…고객확보 부진 영향

![[신추=AP/뉴시스]사진은 대만 신추에 있는 대만 반도체 제조 회사 TSMC 본사 모습. 2023.07.10.](https://img1.newsis.com/2021/11/09/NISI20211109_0018137437_web.jpg?rnd=20230710093307)

[신추=AP/뉴시스]사진은 대만 신추에 있는 대만 반도체 제조 회사 TSMC 본사 모습. 2023.07.10.

삼성전자는 패키징이 중요한 3나노 이하 첨단 공정에서 고객 수주 및 수율 부진 등을 겪으며 뒤처진 모습이다.

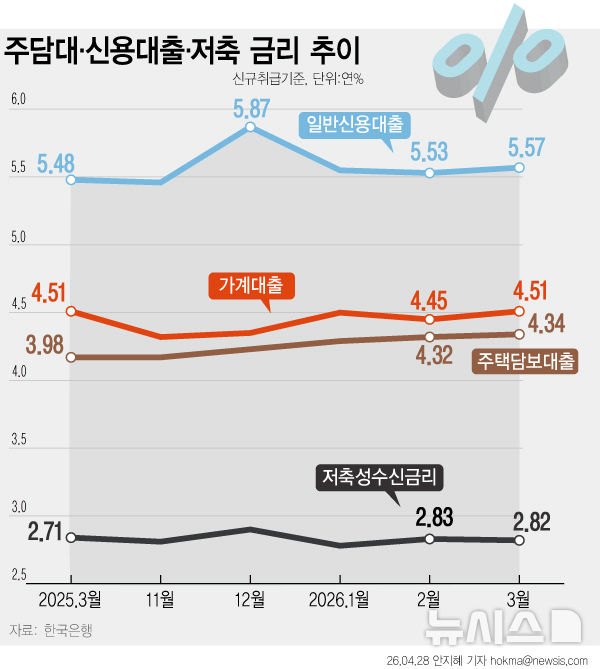

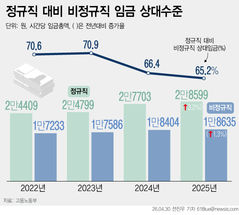

26일 시장조사업체 카운터포인트리서치에 따르면 올 1분기 TSMC의 후공정 통합 파운드리 시장 점유율은 35.3%로 글로벌 1위를 유지했다.

인텔(6.5%), ASE(6.2%), 삼성전자(5.9%) 등 주요 경쟁사들과 30% 안팎의 격차를 보이고 있다. TSMC와 2위의 격차는 지난해 4분기 28.7%에서 올 1분기 28.8%로 소폭 벌어졌다.

후공정 통합 파운드리는 '파운드리 2.0'으로도 불리는데, 단순 반도체 위탁생산 뿐 아니라 패키징, 테스트, 포토마스크 등 후공정 분야를 모두 포함하는 개념이다. 최근 초미세공정의 물리적 한계로 이 후공정 단계가 중요해지고 있다.

TSMC가 순수 파운드리를 비롯해 후공정 통합 파운드리에서도 두각을 나타내는 이유로 독보적인 첨단 패키징 기술력이 꼽힌다.

TSMC는 올해 첨단 패키징 기술인 '칩 온 웨이퍼 온 서브스트레이트(CoWoS)'의 생산량을 전년 대비 2배 이상 늘릴 계획이다. 월간 생산능력은 기존 예상치인 4만 개보다 월등히 많은 7만5000개 수준으로 커진다.

CoWoS는 서로 다른 칩을 기판 위에 수평 연결해 마치 한 몸처럼 동작하도록 하는 TSMC의 자체 패키징 기술이다. 기존 패키징 기술보다 집적도가 더 높아, 칩 속도나 전력 성능 향상은 물론 공간도 줄일 수 있다.

TSMC는 또 다른 차세대 패키징 기술인 '팬아웃-패널레벨패키징(FO-PLP)'에 대한 기술 개발에도 나서고 있는데, 내년 미니 생산라인을 구축할 예정이다. 이는 직사각형 인쇄회로기판(PCB) 패키징을 도입한 기술로, 생산 효율이 높고 비용도 절감할 수 있다.

FO-PLP의 공정 도입이 본격화되면 패키징 분야에서 경쟁사들과의 격차는 더욱 벌어질 전망이다.

반면, 삼성전자는 첨단 패키징 중요도가 큰 3나노 이하 미세공정에서 고객사 확보 및 수율(양품비율) 회복이 더뎌지면서, 후공정 분야에서도 아직 경쟁사들에 뒤처져 있다.

삼성전자는 첨단 패키징을 앞세워 메모리와 파운드리를 한 데 묶은 '턴키(일괄 수행)' 전략을 펴고 있지만 아직 성과는 미진하다.

인텔의 시장 점유율 순위는 지난해 4분기 3위에서 올 1분기 ASE를 제치고 2위로 올라섰다. 여러 칩을 하나의 패키지에 결합할 수 있는 '포베로스'와 전력 효율성을 높이는 '파워비아' 등 기술력을 일부 인정 받은 것이라는 해석이다.

업계 관계자는 "앞으로 후공정 분야는 더욱 중요해질 것"이라며 "특히 패키징은 시장의 게임 체인저가 될 수 있다"고 전했다.

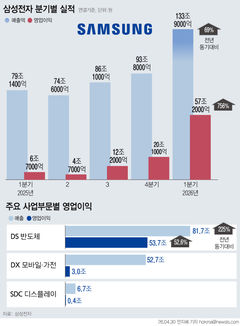

![[서울=뉴시스]카운터포인트리서치의 후공정 통합 파운드리 시장 점유율. (사진=카운터포인트리서치 제공) 2025.06.25. photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2025/06/25/NISI20250625_0001876809_web.jpg?rnd=20250625172239)

[서울=뉴시스]카운터포인트리서치의 후공정 통합 파운드리 시장 점유율. (사진=카운터포인트리서치 제공) 2025.06.25. [email protected] *재판매 및 DB 금지

◎공감언론 뉴시스 [email protected]

Copyright © NEWSIS.COM, 무단 전재 및 재배포 금지