"TSMC, 3나노 가동률 100%…첨단 공정 수요↑"

카운터포인트리서치, 분석 결과

2나노는 100% 도달 더 빠를 듯

이원화 전략으로 美 수요 공략

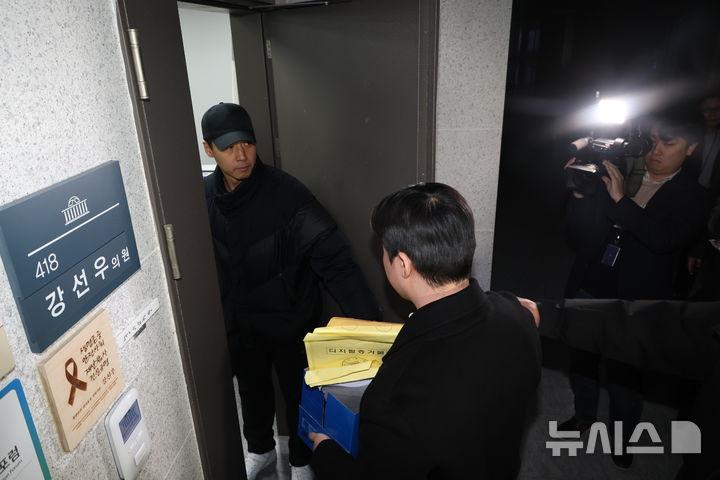

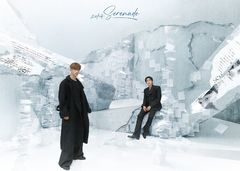

![[서울=뉴시스]AMD는 14일(현지시각) 차세대 AMD 에픽 프로세서인 코드명 '베니스(Venice)'가 대만 파운드리 업체 TSMC의 첨단 2나노미터(N2) 공정 기술로 테이프아웃 및 생산된 업계 최초의 HPC 제품이라고 발표했다.(사진=AMD 제공) photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2025/04/15/NISI20250415_0001818509_web.jpg?rnd=20250415171403)

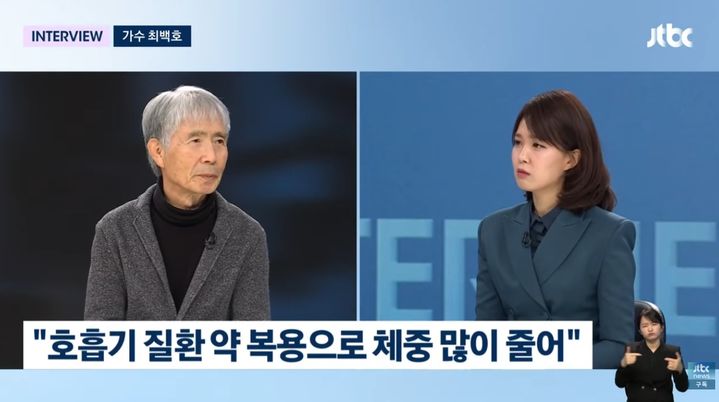

[서울=뉴시스]AMD는 14일(현지시각) 차세대 AMD 에픽 프로세서인 코드명 '베니스(Venice)'가 대만 파운드리 업체 TSMC의 첨단 2나노미터(N2) 공정 기술로 테이프아웃 및 생산된 업계 최초의 HPC 제품이라고 발표했다.(사진=AMD 제공) [email protected] *재판매 및 DB 금지

21일 시장조사업체 카운터포인트리서치에 따르면 TSMC의 3나노미터(㎚·10억분의 1m) 공정이 최근 가동률 100%에 도달했다. 양산을 시작한 이래 5분기 만이다.

올해 양산에 들어가는 2나노 공정의 경우 완전 가동률에 도달하는 속도가 더 빨라진다. 2나노는 양산 이후 4개 분기 만에 가동률 100%에 도달할 전망이다.

이는 역대 다른 공정보다 더 빠른 속도로, 그만큼 미국 소비자 수요 증가가 급속한 것으로 추정된다.

TSMC는 핵심 연구개발과 공정 설계는 대만에 유지하면서도, 미국 내 생산 확장을 서두르고 있다. 현재 애플 외에도 퀄컴, 미디어텍, 인텔, AMD 등 주요 반도체 업체들이 TSMC의 2나노 공정을 도입할 예정이다. TSMC는 미국에서 향후 2나노를 비롯해 차세대 첨단 공정 도입을 검토 중이다.

보고서는 "TSMC는 대만-미국 이원화 전략으로 2030년 이후에도 AI와 HPC(고성능컴퓨팅) 등 첨단 공정에서 높은 가동률을 유지할 것"이라고 전망했다.

◎공감언론 뉴시스 [email protected]

Copyright © NEWSIS.COM, 무단 전재 및 재배포 금지